Today, the mobile phone has become the consumer’s favourite device, carried everywhere and never out of reach morning, noon and night. Even so, it is a fact that for most users most of the time, the mobile phone remains in a quiescent state. While the phone is kept continuously switched on, most of us spend most of the time not actively using our phone. So the phone just sits in our pocket, on the desk or by our bedside, waiting for us to make a call, launch an app or watch a video stream.

This means that the duty cycle of the phone’s applications processor is typically characterised by long periods of very low levels of activity, as the operating system and radio devices tick over in the background, punctuated by short bursts of intense activity. The same pattern may be observed in the low-power DRAM main memory which supports the applications processor: most of the time is spent operating at a low data rate, but there are short periods of high data-rate transfers to the processor.

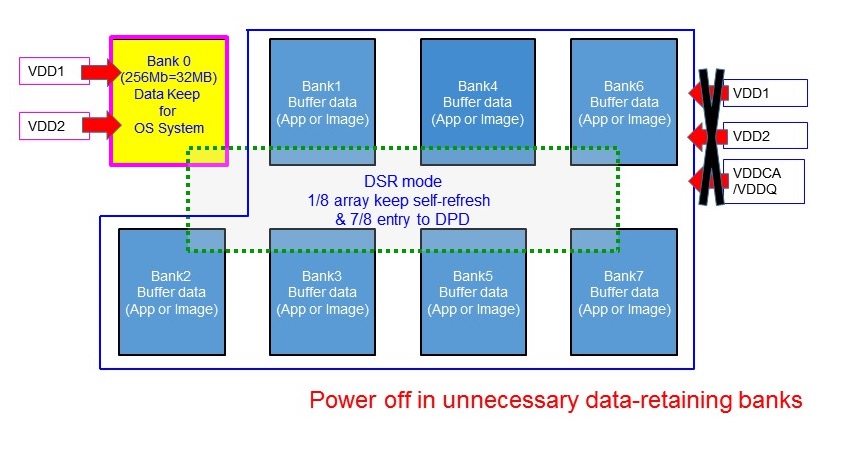

The JEDEC industry standard for DRAM devices does specify a power-saving feature, Partial Array Self-Refresh (PASR), which can be applied when transferring small amounts of data, to avoid refreshing the data in those portions of the memory array that are not being used. Even so, most of the energy consumed by mobile DRAM devices is typically used at low data rates, because mobile DRAM spends so much of its time operating at these low data rates (see Figure 1).

Fig. 1: although a mobile DRAM uses less power (Watts) at low data rates than at high data rates, operation at low data rates accounts for the majority of total energy consumed. (Picture credit: Winbond)F

This means that there is a considerable benefit to be gained from any technology that can reduce power consumption when mobile DRAM operates at low data rates. And now Winbond has developed a new feature that provides a dramatic extension to the power-saving capability of mobile DRAM when operating at low data rates, as this article describes.

Power-saving capability of standard DRAMs

The JEDEC standard for DRAM specifies power-saving features including Automatic Temperature-Compensated Self-Refresh (ATCSR), and configurable drive strength, as well as PASR. These features may be deployed by executing instructions specified in the Extended Mode Register Set (EMRS) also specified by JEDEC. The PASR function is applicable when the data rate is low. It operates on the principle that, when the rate of data transfer between the DRAM and applications processor is low, all of the data in use may be retained in specific banks of memory cells. This allows the device to save the power that would have been consumed by refreshing the remaining banks, since these banks contain unused data.

In a typical mobile phone use case, the operating system code, which is always in use, might be stored in one bank of a typical 256Mbit DRAM, while the multiple other banks which are available for application data do not need to be refreshed when the applications are not in use. While PASR is in operation, all the internal voltage generators inside the DRAM stay in low-power mode.

It is worth noting that the operation of PASR calls for careful partitioning of the always-on data (such as operating system code) from other data types such as application data that are only required periodically.

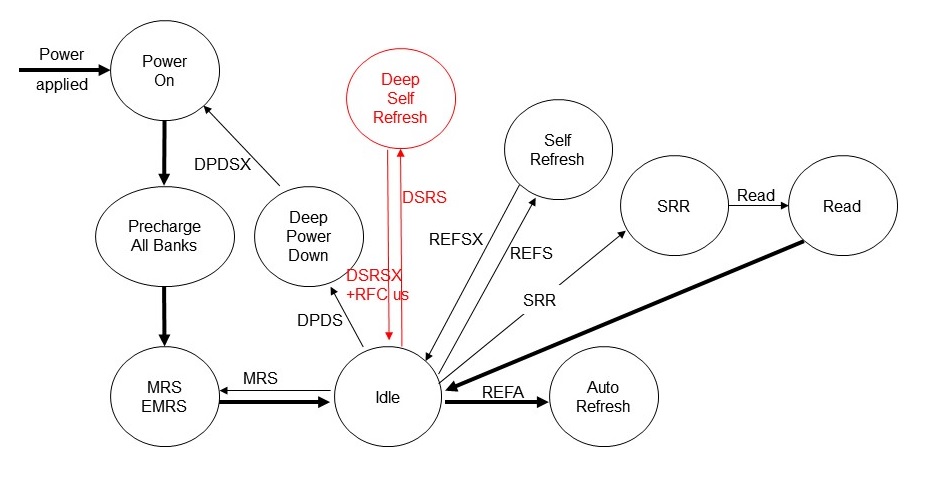

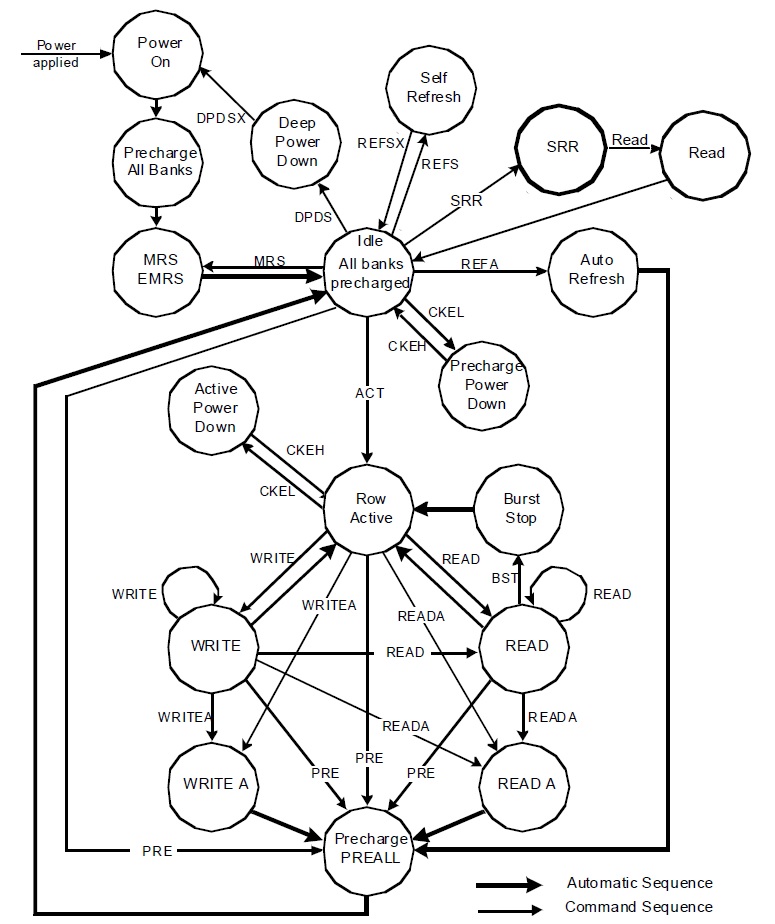

Separately, the JEDEC standard specifies a Deep Power-Down (DPD) mode, in which the entire memory array shuts down. All internal voltage generators inside the device are stopped and all data are lost, as is all the information in the Mode Register Set (MRS) and the EMRS. On exit from DPD into Active mode, the complete re-initialisation process must be executed (see Figure 2). This affects the latency of memory operations: the re-initialisation will cause a delay between the call from the applications processor for a memory buffer, and the buffer becoming available.

Fig. 2: state machine flow diagram for standard JEDEC DRAM devices, showing need to reinitialise device on exit from Deep Power Down State (DPDS). (Picture credit: JEDEC)

New Winbond extended PASR mode

The power savings to be made from the PASR mode are useful but limited. Now Winbond is offering a way to extend the power savings available from PASR by implementing a new Deep Self-Refresh (DSR) mode, which is not specified in the JEDEC standard.

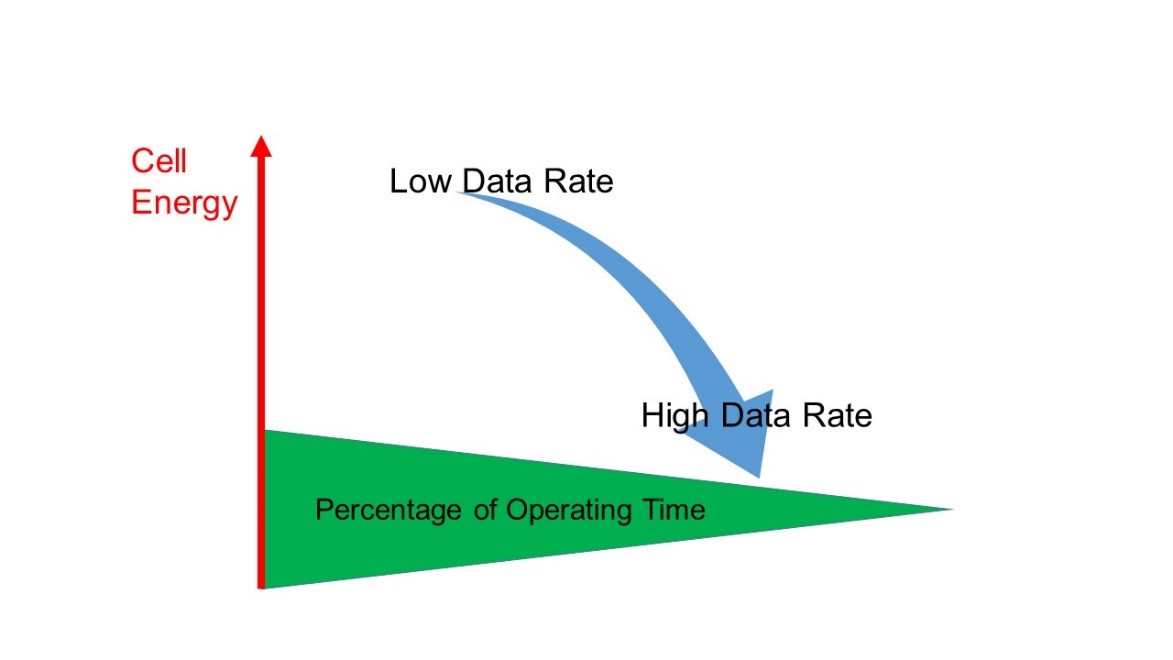

DSR operates in a similar way to PASR at low data rates, allocating used data to one or more banks, in which data are refreshed, and allowing the remaining banks to lose their data by stopping the refresh current from flowing to them. The difference with DSR is that the unused banks of memory cells are allowed to go into a DPD state (see Figure 3).

Fig. 3: extended power saving is possible with DSR mode when seven out of eight banks of cells are allowed to enter DPD state. (Picture credit: Winbond)

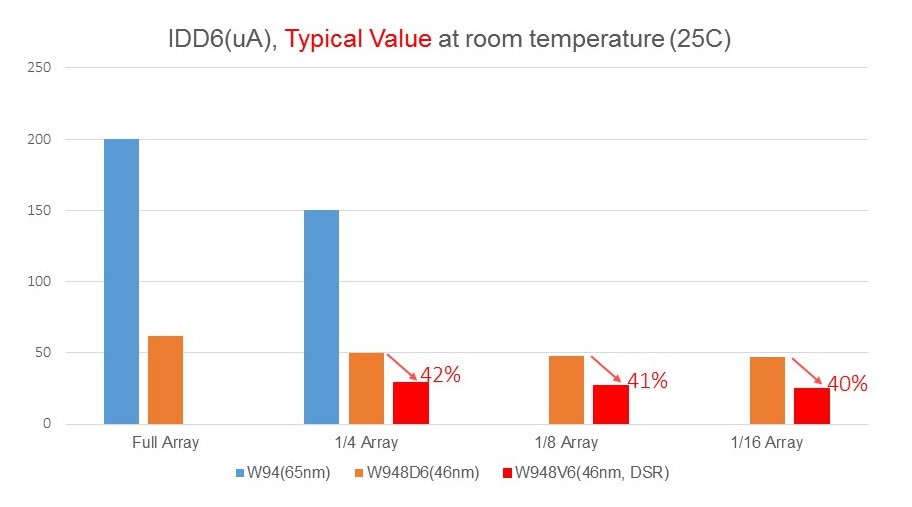

This has the advantage of reducing the total energy used in self-refresh mode even below the level achieved in PASR mode on its own (see Figure 4). In the diagram, the typical current drawn in PASR mode is shown for the W948D6 device from Winbond. Fabricated in Winbond’s newest 46nm process, the W948D6 achieves modest power savings through the standard PASR mode compared to power consumption when the full array is in self-refresh (IDD6) mode. The W948D6 does not offer the new DSR mode – but the 46nm W948V6 does, and the red blocks in the graph show that power falls by 40% or more compared to operation in PASR mode.

Fig. 4: dramatic additional savings available from implementation of DSR mode

The new DSR mode is compatible with the JEDEC specifications, requiring only the addition of (non-standard) instructions to the EMRS. The addition of DSR capability entails no change to the user’s hardware design and no change to the standard JEDEC pin-out. Design teams can migrate from earlier DRAMs to a DSR-enabled DRAM such as the W948V6 without making any change to their board layout, and by implementing a simple additional instruction in the memory controller.

As stated above, in exiting from DPD the memory banks need to be fully re-initialised (see Figure 5). This means that there is some additional latency on switching from DSR to Active mode compared to the switch from PASR mode to Active mode.

Fig. 5: state machine flow diagram showing DSR mode in addition to standard JEDEC modes

Roadmap for roll-out of DSR function

The Winbond roadmap sees the DSR function being introduced into a number of LPDDR devices over the coming months, alongside the 256Mbit W948V6KBHX series which is already in mass production. New devices with DSR capability will include 32Mbit Pseudo-SRAM (PSRAM) parts in the first half of 2018; and 2Gbit 1.8V/1.2V DDR2 DRAM parts in the second half of 2018.

These new parts offering the DSR option will give manufacturers of mobile phones and other battery-powered devices a new means to reduce total energy use attributable to the DRAM and take advantage of additional power savings when the device is operating at a low data-transfer rate.

By Hsiu-Min, Lin

DRAM Product Marketing Manager, Winbond Electronics Corporation