消费者对于产品的要求已经不满足于现状,在行动运算装置上,不断追求功能更多且更轻薄的产品。从前需要在笔电上作业的工作,现在早已经可以在智能型手机上完成。更不用说现在的智能型手表还能透过跟智能型手机连结而做到以前想象不到的事情。

在许多非常在意微小化电路空间的设计中,随着数据量的增加,储存器占用的空间对于微型化设计来说非常的关键。闪存的NOR通常用来储存开机程序,而NAND通常用来储存大量数据。在电路板设计时,都必须为这些闪存IC预留焊接空间。

串行式NOR和NAND闪存因为脚位少,更有利于微小型系统的设计。而华邦电子所生产的串行式NOR和NAND闪存约占全世界出货量的30%,在串行式闪存的出货量更是世界第一。华邦电所发明的 Quad Serial Peripheral Interface (QSPI) 是带宽更高、更高速的传输接口,可用来取代传统多脚位并列式闪存的应用,譬如,用于微控制器和主芯片之间的连接。

为了符合微型化趋势的设计理念,华邦电提出了创新的应用方法,把串行式闪存NOR和NAND芯片堆栈在同一个芯片封装中。 这个方法取代了在电路设计中,必须要使用两个单独芯片,进而能节省电路设计的空间。

在这篇文章当中,主要说明了在传统上使用上,两个或多个堆栈芯片的应用情境中所会遭遇到的瓶颈与难题,并说明如何藉由华邦电所提出的堆栈芯片解决方案来解决这些问题,来进一步提高产品的效能!

使用堆栈内存芯片的好处

通常在一个小型的装置会使用一个16Mbit的NOR闪存来储存开机程序,,另外会用另一个1Gbit的NAND闪存来储存数据或操作系统。NOR闪存具有快速读取的优势,可让系统进行随机存取,适用于需要经常快速读取数据的应用。而NAND闪存具有较快的写入速度,价格上也较512Mbit以上的NOR闪存来的便宜。

现行一般的设计大都是使用个别的NOR和NAND闪存来和主芯片连接。

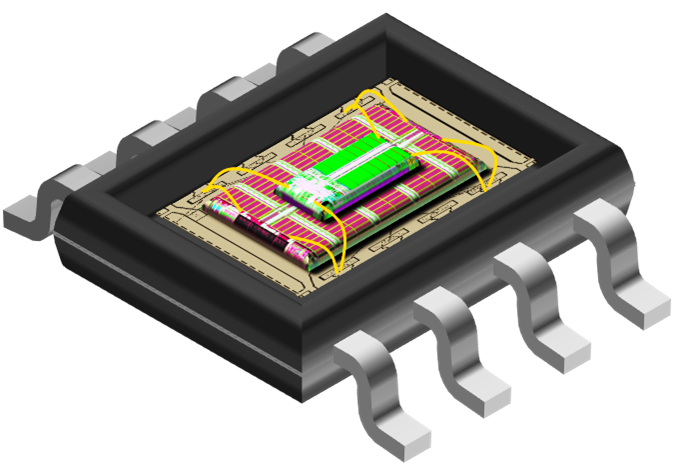

然而现行分别使用两个内存的设计能透过华邦提供的SpiStackTM系列堆栈产品 (如下图1) 来达成相同的设计结果。好处是能使电路板设计上减少一个内存组件,让电路设计更有弹性进而减少电路板的大小。

图1. 外观尺寸较小的NOR闪存堆栈在NAND闪存上方。两个芯片透过封装打线固定在基板上。

应用上除了NOR加上NAND的堆栈,还可以是NOR加NOR或是NAND加NAND的堆栈组合。例如原来设计是用512Mbit的NAND需要扩增到1Gbit,但有可能1Gbit NAND的封装尺寸可能与原先使用的512Mbit不一样,导致需要更改电路板设计。而使用华邦这样有弹性的堆栈芯片组合,用两个512Mbit NAND加NAND的芯片堆栈在原来的封装中,不但可以让内存容量增大为两倍,还省去重新设计板子的问题。

堆栈芯片的主要概念是要减少芯片脚位,让电路设计简化和减少重新设计所需的工作。不过华邦推出的堆栈芯片方案不但能够完全不增加芯片脚位来维持电路设计的弹性,还能进一步改善读写效能。

低脚位数的堆栈芯片方案

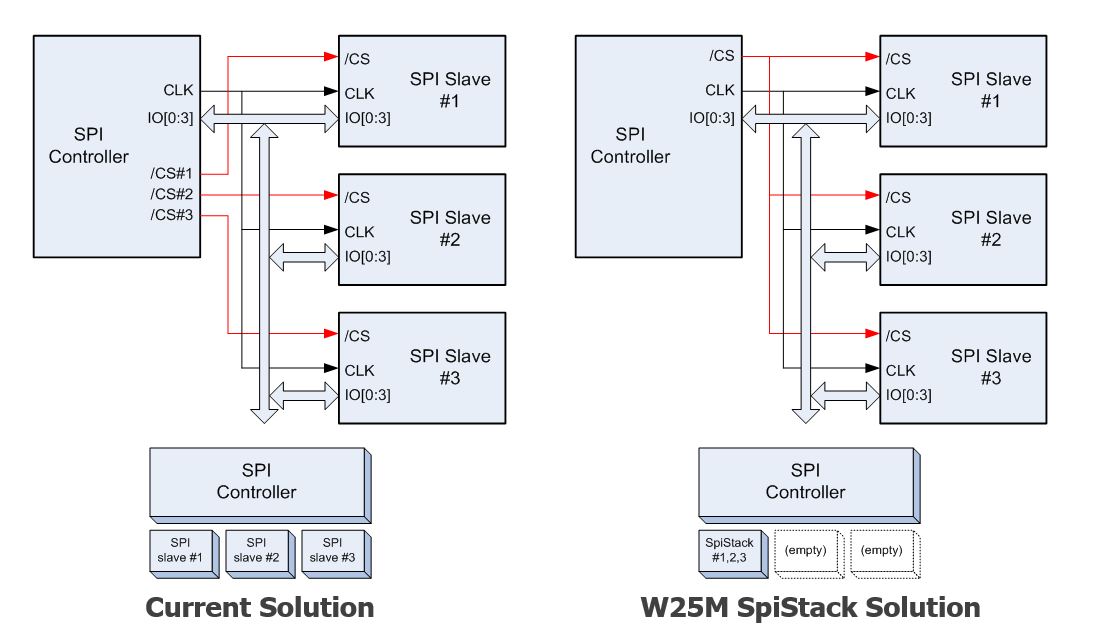

堆栈芯片一个主要的挑战在于:如何让主芯片或微控制器跟堆栈在同一个封装里面的闪存作沟通。为了避免在SPI通讯接口上的冲突,主芯片会透过芯片选择(CS)的硬件讯号来选择要存取的SPI接口闪存。

在其它厂家的堆栈芯片作法,芯片选择(CS)是透过硬件讯号来实现,所以若是两个芯片的堆栈就需要两个芯片选择(CS)的脚位,若是三个芯片的堆栈就需要三个芯片选择(CS)的脚位,依此类推。

显然地这样的堆栈芯片作法,增加了很多芯片选择(CS)的脚位,当然在电路板上也需要较多的空间给这些讯号线。

图2. 堆栈芯片用软件方式来实现芯片选择(CS),仅需要一根芯片选择(CS)讯号。

然而透过华邦最新推出的W25M SpiStackTM系列闪存,可以解决这个问题,主芯片藉由使用软件的方式透过一个芯片选择(CS)的指令来选择要存取的闪存芯片 (如图2)。 在堆栈芯片里的每一个芯片都有独立不冲突的标识符(ID),透过标识符(ID)可让软件执行芯片选择(CS)并知道现在正在存取的芯片是哪一个。

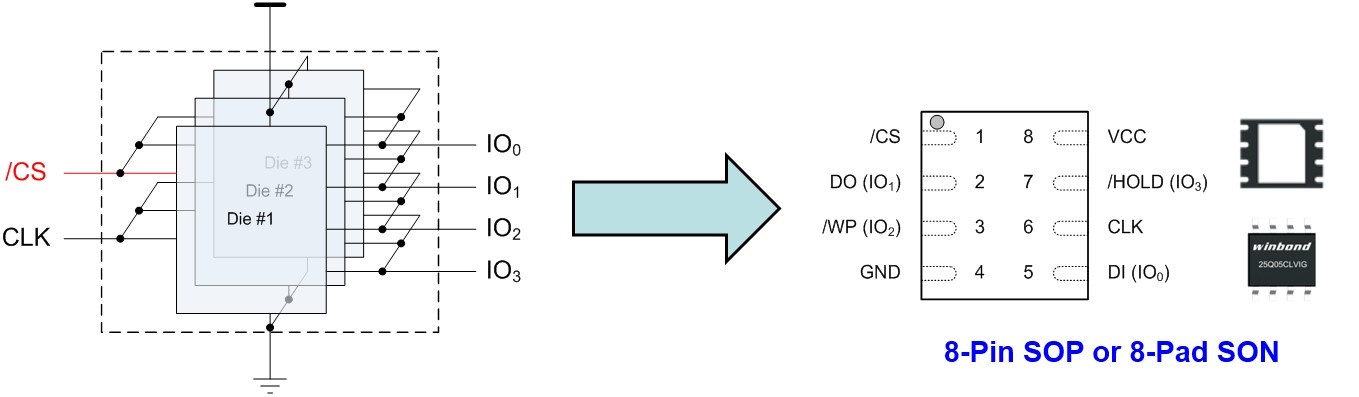

因为是透过软件的方式由一个芯片选择(CS)的指令来选择要存取的闪存芯片,可让2~4个芯片封装在标准的8-pin SOP 或 8-pad SON 封装中 (如图3)。然而其他厂商堆栈芯片的作法必须多出相对应的芯片选择脚位(CS),因而通常需要使用16-pin SOP or 24-ball BGA 相对尺寸较大的封装而增加电路设计的复杂度。

图 3. 透过软件实现方式让3个堆栈芯片可以封装在一个8-pin脚位的封装中。

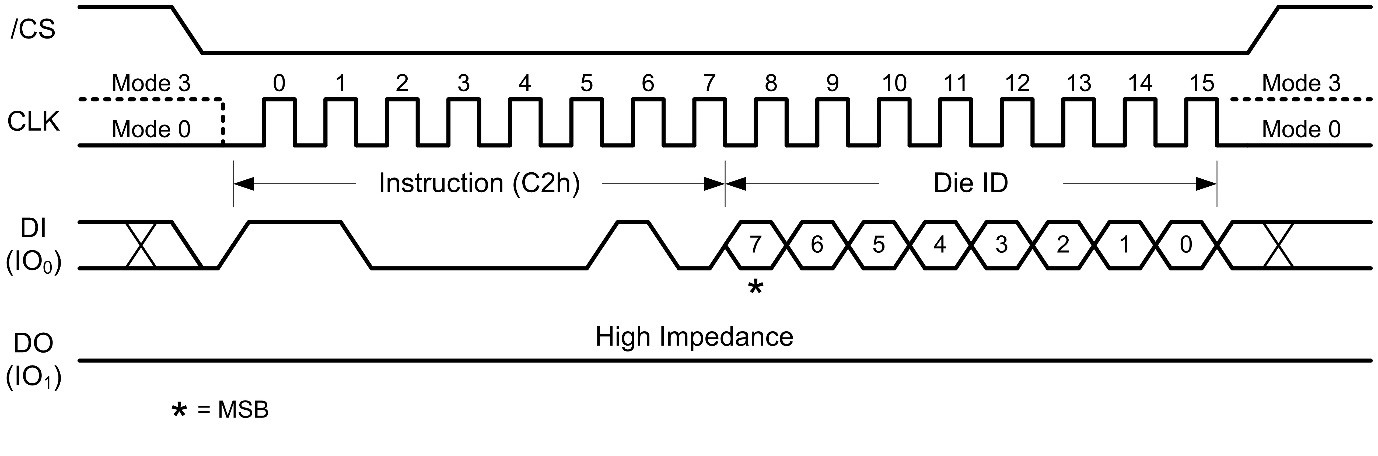

对于开发者而言,要实现华邦SpiStackTM的多芯片选择(CS)指令相当容易。 “C2h”指令可用于选择任一堆栈芯片来存取 (如图4),不管现在芯片状态为何,都可在任一时间作切换去选择芯片。

图4. 在C2h指令使用各芯片的唯一标识符作选取。

如何达到较快速的读取和写入操作效能

相较于SRAM和DRAM而言,写入速度慢是闪存本质的特性。系统常遇到的一个情况是当要读取闪存时,若刚好先前有执行过写入的指令,这时若要读取闪存则需要等待写入程序的完成,如此一来就浪费系统在等待的时间。另一个作法是执行指令让写入程序先暂停,等待读取完所需的数据后,再执行回复写入指令让先前未完成的写入程序继续执行,但这样的作法不但让执行上变的复杂,也拖慢真正要读取与写入的时间。

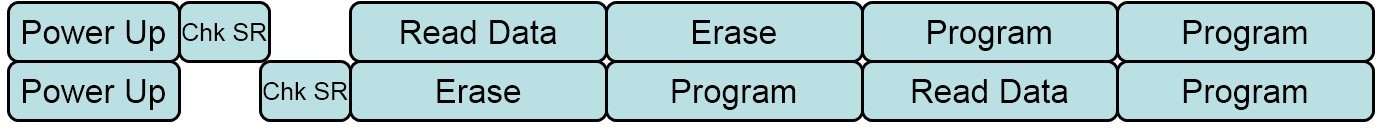

华邦推出的堆栈芯片可以透过同时操作避免掉前述的问题。也就是当一个芯片正再进行写入或擦除的程序时,可以同时间的去读取另外一个芯片 (如图5)。

图5. 在华邦闪存的两个堆栈芯片中,当一个芯片在执行写入或抹除时,主芯片可以对另外一个芯片同时去作读取、 写入或抹除的程序。

如同先前的叙述,在SPI接口上同一时间一次只能选取到一个芯片,但是华邦SpiStackTM技术是可以让两个芯片同时进行操作。例如,当一个芯片在进行写入或抹除程序时可同时对另一个芯片作读取,或是当一个芯片在进行写入或抹除程序时也可对另一个芯片同时下达写入或抹除的指令。

在很多的应用中,若能够使用同时操作的程序就能够大幅提升记忆体操作的效能。 这代表华邦SpiStackTM在操作上能够比其他只能单一执行一个程序的操作方式更快更有效率。

提供同质与异质的闪存堆栈搭配组合

华邦的SpiStackTM堆栈芯片解决方案提供客户多种的闪存容量与封装组合,包含同构型的内存堆栈(例如NOR+NOR 或 NAND+NAND) 或是异质性的内存堆栈 (例如 NOR+NAND) 等组合。华邦作为世界级的内存设计和制造商,能够提供最多样化的产品组合来满足客户对内存容量和封装的需求。

有弹性的设计和使用普遍的封装是开发设计者对于选用内存的重要考虑, 这样目的是可以让之后的设计可以直接更换不同容量的内存而不需要作电路的变更。

目前已经可以供货的SpiStackTM堆栈芯片产品包含:

- a 16Mbit NOR + 1Gbit NAND

- a 32Mbit NOR + 1Gbit NAND

- a 64Mbit NOR + 1Gbit NAND

- a 128Mbit NOR + 1Gbit NAND

- a 512Mbit NOR consisting of two 256Mbit NOR dies

- a 2Gbit NAND consisting of two 1Gbit NAND dies

更多在2018年即将供货的产品组合在华邦电子的SpiStackTM产品型录当中,其中也可透过客户提出的需求来计划供货。

本文作者: 华邦电子 资深策略市场营销处长K. C. Shekar, 专业副理 Takehiro Kaminaga