Internet of Things (IoT)の世界では、何億もデバイスが世界中のネットワークに接続されることが予測され、IoTノードの数は莫大になるといわれています。数学的に考えれば、1ノード当たりの平均製造コストを抑える必要があり、そうでなければ、IoTは実現不可能なものとなるでしょう。今日、エレクトロニクス業界の多くのサプライヤは、1ノードあたりのBOM(bill-of-material)コストは平均5ドルを超えないよう努力しています。

つまり、デバイス設計者は極度なコスト制限を受けることになります。家庭やオフィスで使用されているIoTノードの中には、すぐに利用できるWi-Fi®やBluetooth®等、ワイヤレス接続ができるものがあります。家電製品で広く使用されているこれらの技術は、市販のコンポーネントを用いることで、エンドノードに安価で実装できます。

しかしながら、屋外で使用されるものを含む一部アプリケーションは、Wi-FiまたはBluetoothを用いてインターネットアクセスポイントに接続することができません。その場合、Wi-FiまたはBluetooth接続で利用可能な最大100m以上の広範囲で使用可能な、他の標準技術を使用することとなります。

近年、LPWA(省電力ワイドエリア無線ネットワーク)では、LoRaWAN、SIGFOX、NB-IoTなど、さまざまな技術が利用されています。これらのテクノロジでは、市販の使い慣れたチップセットが利用できない、もしくは一般的なWi-FiやBluetoothシステムオンチップ(SoC)に比べて、少量で出荷されています。

したがって、LPWANに接続するIoTノードの設計者は、コスト面で厳しい問題に直面しています。また、無線に高いコストがかかってしまうと、回路内の残りのコンポーネントに費やせるBoMコストは、さらに制限されてしまいます。残りのコンポーネントの中でも、メモリは最も高価であり、コスト最適化に大きく影響するのです。

この記事では、LPWAN無線を搭載したIoTエンドノードの設計者が利用できるメモリアーキテクチャの選択肢について説明し、パフォーマンス、メモリ容量、システムサイズに対するシステムの要件に応じたさまざまな外部フラッシュメモリソリューションの利点について説明します。

典型的なアプリケーション要件

内部および外部メモリの容量設定は、システムの機能要件に照らし合わせる必要があり、サポートされるアプリケーションによって異なります。 LPWAN接続のアプリケーションは多数ありますが、デバイスタイプの使用例は下記の通りです。

- 環境センサー装備のスマート街路灯

- 一時的な交通信号や建設機械など屋外で使用される移動可能な貴重な資産

- 農業機械または家畜

これらの使用例において、SoCまたはマイクロコントローラは、アプリケーションコードだけでなく、システム管理機能を実行します。これには、コードストレージ用、データ構成用、およびユーザー(アプリケーション)データのためのメモリ要件が伴います。

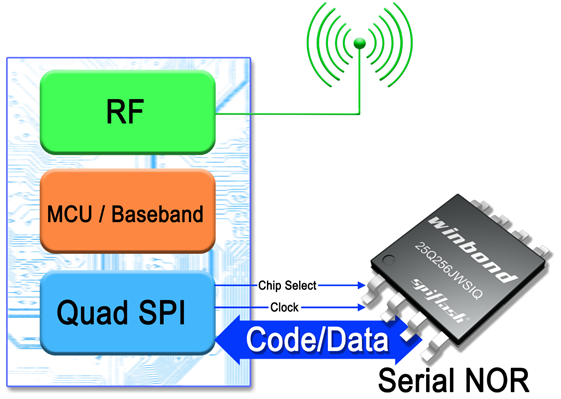

図1: シリアルNORフラッシュメモリに接続する低コストのLPWAN SoC

パフォーマンスを大きく左右し、少ないBoM予算に制限されることのないアプリケーションにおける典型的なメモリアーキテクチャの特徴として下記が挙げられます。

- SoC向けスクラッチパッド用メモリとしてのハイスピードDRAM

- SoCに組み込まれたフラッシュメモリ

- データ構成およびデータ使用におけるストレージ容量要件に応じたNORフラッシュまたはNANDフラッシュデバイス等外部不揮発性メモリIC

しかし、IoTのシステム設計者はコスト最適化の要件に振り回されつつも、最新世代の外部フラッシュメモリデバイスによって提供されるさまざまなアーキテクチャオプションに関心が高まっています。図1はそのアーキテクチャの1つである、 ウィンボンドの 1.8Vspiflash®デバイスを備えたLPWAN SoCを示しています。

よりハイスピードなシリアルフラッシュ

コストに敏感なIoTノード設計者は、データ転送速度が非常に高速なシリアルフラッシュデバイスを利用することで、従来モデルとは異なるアーキテクチャを実装することが可能です。今日のシリアルフラッシュメモリの高速化により、IoTノードの設計者はほとんどの場合、DRAMスクラッチパッドメモリを排除し、内部フラッシュ容量を最小限に抑えた低コストのSoCを使用することができます。このようなフラッシュベースのアーキテクチャは、アプリケーションに必要な性能を維持しながらも、コンポーネント数や、システムサイズ、BoMコストを削減します。

シリアルフラッシュメモリが、DRAMから置き換えられるほど十分なデータ転送速度を持つというのは、一見意外に思えるでしょう。シリアルフラッシュメモリの主なメリットは、高信頼性の不揮発性ストレージ容量を非常に少ないピン数および小パッケージにて提供することですが、理論的には、ピン数が少ないほど処理能力が低くなります。一方、パラレルフラッシュに関しては逆の事が言えます。非常に高い処理能力とデータ速度のために多数のチャネルを供給しますが、そのためには多くのピンが必要となり、ボートのフットプリントは、大きくて複雑なものになってしまうのです。

しかし、シリアルフラッシュメモリーの設計者は長年、小パッケージの外形を維持しながらも、データ転送速度を上げるための方法を開発してきました。現在、QSPI(Quad Serial Peripheral Interface)またはQP(Quad Peripheral Interface)テクノロジを搭載し、最高133MHzの速度で動作するシリアルフラッシュデバイスは最大66Mビット/秒のデータ転送速度を実現します。これは、SoCまたはプロセッサが外部フラッシュメモリからDRAMにシャドーイングせずにアプリケーションコードを直接実行するエグゼクティブ・イン・プレース(Executive-in-Place/XiP)機能に十分対応しており、DRAMデバイスを完全に排除することが可能です。QSPIやQPI機能を備えた高速シリアルフラッシュは、頻繁に実行される機能に対して擬似キャッシュ実行の実装が可能で、パフォーマンスの向上につながります。

シリアルフラッシュデバイスのメモリアドレス範囲は、コードとデータの別々のセクションに分割できるため、すべてのシステムのストレージ要件を満たすことができます。ファームウェアはコードセクションに、ユーザーデータと構成設定はデータセクションに格納されます。

データセクションに格納された情報は常に消去され新しいデータに置き換えられるため、このセクションでは多数のプログラム/イレーズサイクルをサポートする必要があります。 NORフラッシュとNANDフラッシュの2種類のシリアルフラッシュのうち、NOR型は本質的にNAND型より堅固な技術であり、エラー訂正コード(ECC)不要で正確な動作が可能です。 ウィンボンドが提供するすべてのシリアルNORフラッシュデバイスは、最低100,000回の書き込み/消去サイクルに対応しています。

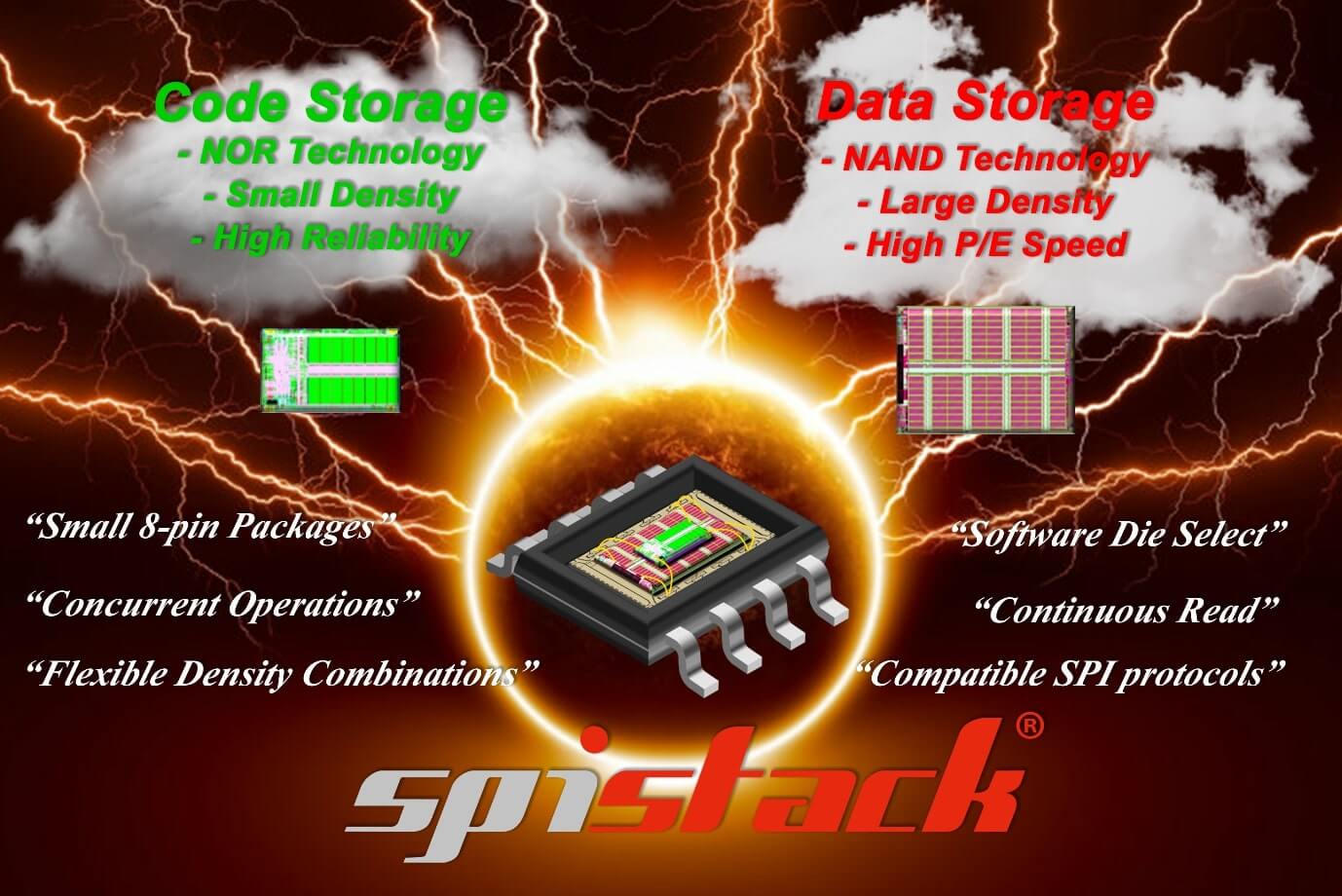

図2:SpiStack®製品内でスタックされるシリアルNORフラッシュダイとNANDフラッシュダイ(画像著作権:ウィンボンド)

512Mビット未満のフラッシュメモリ容量を使用するアプリケーションでは、シリアルNORフラッシュが最もコスト効率に優れ、 512Mビット以上では、通常、シリアルNANDフラッシュがより安価なオプションになります。NANDフラッシュメモリは動作管理のためにコントローラを必要とし、ランダムメモリロケーション内のエラーを検出および訂正し、エラー箇所の再配置、またはエラーのない新しい箇所へマッピングするなど、エラーを含むメモリのブロックを操作(バッドブロックマネジメント)しているのです。

ウィンボンドのシリアルNANDフラッシュ製品は、512Mビット、1Gビット、および2Gビットの容量にて提供可能で、外部のNANDコントローラが実行するべきタスク数を減らす機能を備えています。内部ECCやバッドブロックマネジメントもそれらの機能と言えます。 ウィンボンドの NANDフラッシュは、528ビットごとに1ビットECCを提供します。この、 1ビットECCを備えたウィンボンドのシリアルNANDは、最低10万回のプログラム/イレーズサイクルに対応しています。

シリアルNANDフラッシュ内のバッドブロックマネジメントにより、内部ルックアップテーブル(LUT)の設定に従いバッドブロックへのリードアクセスを正常なブロックに自動的に再マップすることが可能です。 LUTは最大20のリンクを持つことができます。LUTを介したこのバッドブロックアクセスの再マッピングにより、ページ全体や、シリアルNORのような全メモリ範囲での連続読み出し動作が可能になります。これは、限られたページ・リード・アクセスのみを提供し、リード・スループットのパフォーマンスが低下してしまう他社のシリアルNAND製品と異なります。

IoTゲートウェイ設計者の第三の選択肢として、単一パッケージ内に複数のフラッシュメモリダイを組合わせてスタックすることが挙げられ、ウィンボンドのSpiStack®製品)にて実現可能です(図2参照)。SpiStack® は、2つ以上のNORフラッシュダイ、2つ以上のNANDフラッシュ、またはNORダイをNANDと組み合わせる等、様々な構成に対応しています。 SpiStack®は、高信頼性コードストレージ用のシリアルNORフラッシュと、データストレージ用にシリアルNANDフラッシュの組み合わせにより、8mm x 6mmの8ピンWSONパッケージが標準的な構成です。このソリューションは、ピン数を少なく抑えながら、オプション/容量がフレキシブルであるというフラッシュメモリの利点を活かした製品です。また、SpiStack®は、単一の8ピンパッケージと1つのチップセレクトピンを備えています。ウィンボンドのソフトウェアダイセレクション'C2h'コマンドがアクティブダイを選択することで単一チップセレクトピンが供給されます。

シリアルNOR、シリアルNAND、およびSpiStack®製品は、LPWAN経由で接続されるIoTノードに十分なメモリ容量帯を取り揃えています。たとえば、LoRaWANノードは、通常、3Vまたは1.8Vで動作する16Mビット以下の低容量シリアルNORフラッシュを必要とします。NB-IoTを介して接続するノードは一般的に32Mビットから128Mビットの、より大容量のシリアルNORフラッシュを必要とし、1.8V以下で動作されます。一方、アプリケーションによっては1Gビット以上のデータ容量を必要とすることもあり、その場合はシリアルNANDフラッシュやSpiStack®メモリが最適です。

LPWAN接続を使用するIoTノードはモバイルであり、その多くはバッテリ駆動であるため、電力消費の問題はシステム設計者にとって大きな懸案事項です。どのサプライヤも標準的に3Vまたは1.8VのシリアルフラッシュICを提供しており、1.8V品は、アクティブモードおよびスタンバイモードで低消費電力な仕様となっています。

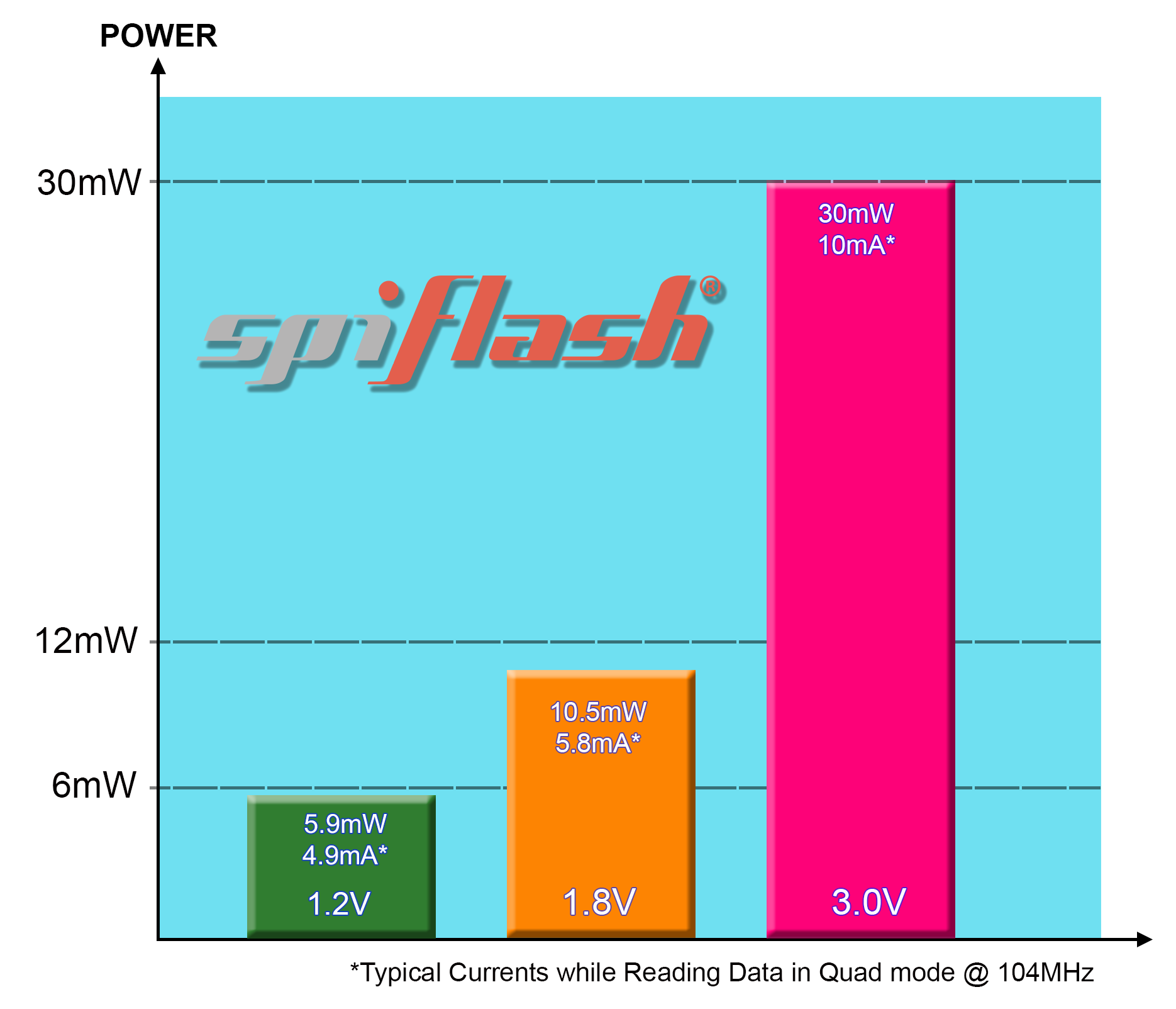

*104MHzクワッドモードにてデータ読込にかかる標準的電力

図3:ウィンボンドのシリアルNORフラッシュICのアクティブリード電流性能評価 / 緑が1.2V新製品(画像著作権:ウィンボンド)

2017年6月、ウィンボンドは新たな超低電力シリアルNORフラッシュICを発売しました(図3参照)。1.5V製品が1.14Vから1.6Vの広い動作電圧範囲を持つのに対し、1.2Vの新製品は1.14Vから1.3Vの動作電圧範囲なので、バッテリが新しい時、また、使用や時間の経過とともに電圧が低下した時の両方においてのバッテリ動作持続性というメリットを、設計に与えてくれます。新しい低電圧品は、1Mビットから128Mビットまでの広い容量幅を取り揃えており、消費電力は104MHzアクティブモードでわずか4.9mA、パワーダウンモードではわずか0.5μAです。

ハイスピードシリアルフラッシュによるコストとスペースの節約

設計者は、ハイスピードなQSPIまたはQPIシリアルフラッシュを使用しXiPを実装することで、DRAMのない設計を構成することが可能になり、スペースの節約およびコンポーネント数とコスト削減につながります。また、SpiStack®などのスタックド・ダイ製品や、バッテリ駆動のアプリケーションで、低消費電力の新しい1.2Vおよび1.5VシリアルNORフラッシュデバイスを使用することで、さらにスペースを節約できます。

このように、最新のシリアルフラッシュ製品を使用することは、LPWAN接続のIoTノード設計者の、パフォーマンス要件を満たすとともに、システム全体のBoMコストを5ドルにするという厳しい目標達成に貢献します。

著:ウィンボンドエレクトロニクスアメリカ、テクニカルマーケティングマネジャー、Conrado Canio