Massive IoTの活況

エリクソンが2020年6月に発表したモビリティレポートによると、NB-IoTやCat-Mを含むMassive IoTが世界中で展開され続けています。しかし新型コロナウィルス感染症が輸送を阻んでいるため、普及の進み具合は予想よりも遅くなっています。IoTアプリケーションのほとんどは、未だに2Gまたは3Gテクノロジーを介して接続されています。2019年には、Massive IoTアプリケーションの数が3倍に増加しており、2020年末までには約1億件に達すると言われています。

エリクソンによると、2025年末までにNB-IoTとCat-Mが全セルラーIoTデバイスの52%を占めると予測されています。中でもアジア地域が最も急速に成長している市場で、2026年までにこの地域のデバイス出荷台数は全出荷台数の67%に増加すると予測されています。

3GPP規格の進展については、NB-IoTまたはCat-Mにかかわらず、リリース15で安定性と応用分野が強化されています。2020年7月3日に確定されたばかりのリリース16では、ネットワークの効率性をさらに強化し、現行のNB-IoTを5G環境で運用できるように展開します。将来的には、リリース17で、帯域幅の集約と低遅延の仕様を拡張し、継続して潜在的なアプリケーションの開発と探求を行い、5G NRの設立によりセルラーIoTの普及を促進します。

IoTに対する半導体ベンダーのアクション

IoT分野では、市場で広く採用されるために、低コスト、低消費電力、コンピューティング効率など様々な設計上の考慮点が満たされる必要があります。特に、スマートスピーカーやスマートメーターなどのバッテリー駆動デバイスでは、豊富なIoT機能や使いやすいヒューマンインターフェースに加え、バッテリー持続時間が成功のカギを握るようになってきています。そのため、低消費電力化が重要性を増しています。長時間のバッテリー持続時間を実現するためには、低消費電力のMCUを採用することに加え、その他の低消費電力の周辺部品も考慮する必要があります。

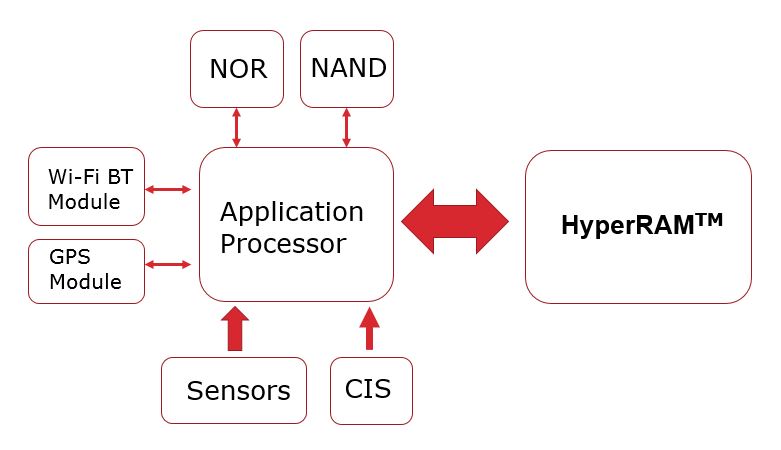

モバイルデバイスの多くは、図1に示すようなアーキテクチャを備えています。タブレットやスマートウォッチがこれにあたります。Wi-Fi/BTとセルラーモジュールが通信を担っています。センサー(タッチパネルなど)は、外部の情報を収集し、アプリケーションプロセッサーに情報を転送するために使用されます。NOR/NANDフラッシュメモリはコードやデータの格納に用いられ、DRAMは一時的な処理に使用されます。

上述を踏まえ、多くのMCUメーカーは、市場の需要に応えるために、より高性能で低消費電力の新世代MCUを開発しています。また、システム全体の設計の観点から、MCUと連携するDRAMにも、既存のSDRAM、低電力SDRAM、CRAM/PSRAMよりも優れた利点を提供する新しいオプションが求められています。これらの既存DRAM規格は、かなり以前から定義されているものであり、表1のように最新テクノロジーについていくことができませんでした。

図1 モバイルデバイスのブロック図

| SDRAM | LPSDRAM | CRAM/pSRAM | HyperRAM™ | |

|---|---|---|---|---|

| 規格発行時期 | 1994 | 2007 | 2005 | 2019 (2.0), 2014 (1.0) |

| 規格発行時のロジックプロセスノード | 800nm | 65nm | 90nm | 7nm |

表1DRAMテクノロジー年表

HyperBus™インターフェースに対応するHyperRAM™は、この需要に応えるための最新の技術的解決策です。HyperBus™テクノロジーは2014年に初めてサイプレスによって発表され、2015年には初のHyperRAM™製品が発売されました。今後の市場の伸びが期待できると考え、ウィンボンド・エレクトロニクスは、本製品の市場に参入することを決定し、32Mb/64Mb/128Mbの容量帯にてHyperRAM™を開発し、販売を開始しました。

HyperRAM™を使用するメリット

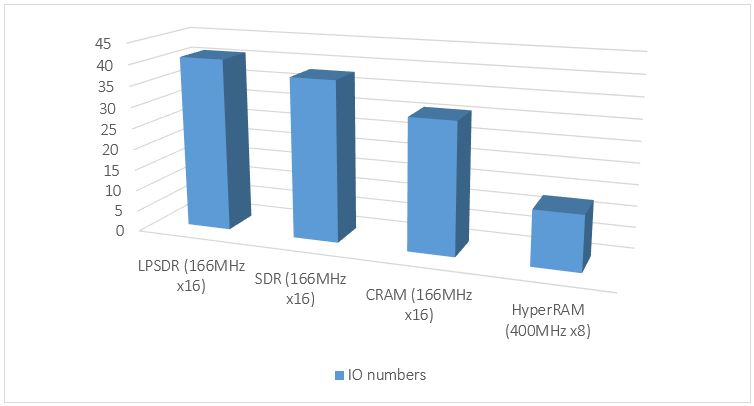

HyperRAM™は信号IOピンが13本しかないため、PCBレイアウト設計を大幅に簡素化できます。また、最終製品を設計する際には、MCUが他の目的のためにピンをアサイン出来たり、MCUシステムをより少ないピンで構成することで費用対効果を高めたりすることができます。図2に示すように、HyperRAM™は、Low Power SDRAMやSDRAM、CRAM/PSRAMなどの類似DRAMと比較して、最少のピン数でほぼ同じスループット(333MB/s)を達成できます。

図2 IOピンの比較

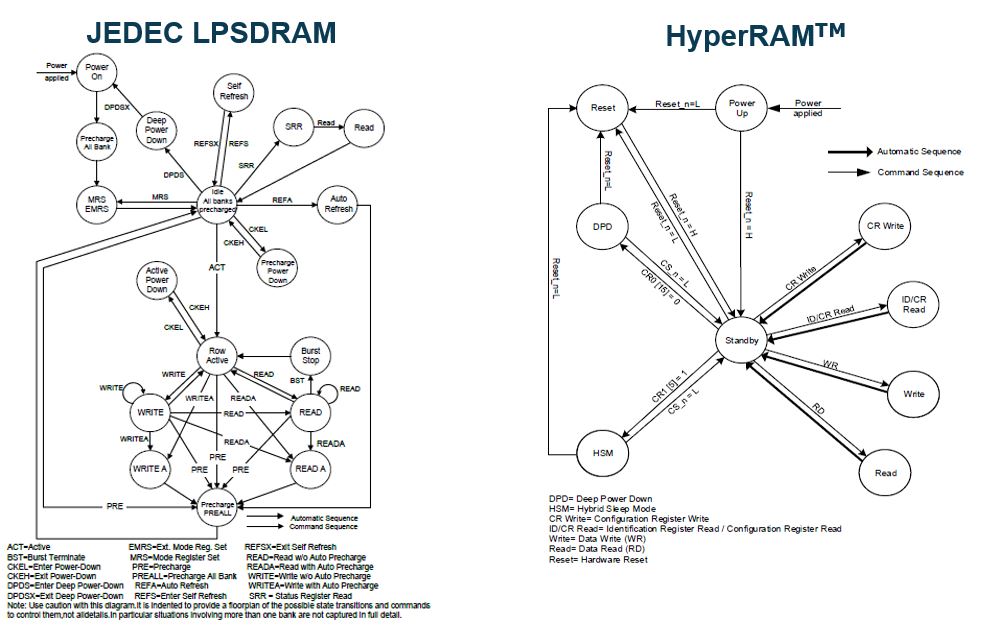

制御インターフェースの簡素化もHyperRAM™の特徴です。Low Power SDRAMが18のステートを持つのに対し、PSRAMは9ステートしかありません。フローステートが少ないほど、DRAMコントローラの複雑さを軽減することができます。その詳細な違いを図3に示します。

例えば、PSRAMアーキテクチャをベースにしたHyperRAM™は、セルフリフレッシュ型のRAMです。さらに、自動的にスタンバイモードに戻ることができます。そのため、システムメモリを使いやすくなり、ファームウェアやドライバの開発も簡素化されます。

図3 Low Power SDRAMとHyperRAM™のステートフローの違い

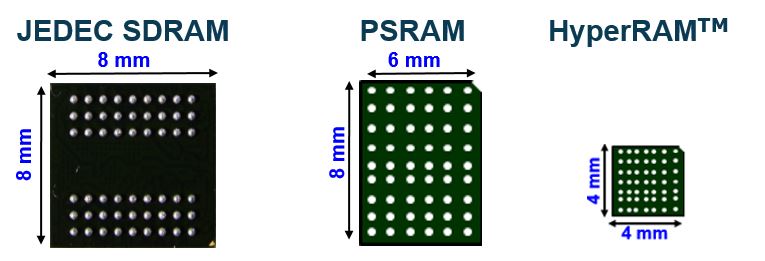

近年開発されたHyperRAM™は、最新の半導体プロセスノードとパッケージテクノロジーを利用しており、パッケージサイズは他のどのDRAMよりも小さくなっています。図4では、JEDECで定義されているSDRAMとPSRAM、HyperRAM™のサイズを比較しています。

図4 パッケージサイズ比較

IoTデバイスへのカギ

IoTデバイスは通常、バッテリーから電力を供給されているため、消費電力が非常に重要です。消費電力を抑えることは、使用されるエネルギーの節約だけでなく、充電や電池交換のコスト削減にもつながります。ウィンボンドの64MビットHyperRAM™を例にとると、スタンバイ時の消費電力は90uW@1.8Vですが、同じ容量のSDRAMでは約2000uW@3.3Vとなっています。さらに重要なのは、HyperRAM™の消費電力はハイブリッドスリープモードでわずか45uW@1.8Vであり、スタンバイモードのSDRAMにおける消費電力と大きな差があることです(表2)。一方、Low Power SDRAMを採用した場合でも、消費電力、フォームファクタともにHyper RAM™よりも大きくなっています。

| SDRAM | CRAM | LPSDRAM | HyperRAMTM | HyperRAM™ (ハイブリッドスリープモード) | |

|---|---|---|---|---|---|

| 電圧(V) | 3.3 | 1.8 | 1.8 | 1.8 | 1.8 |

| スタンバイ電力(uW) | 2000 | 400 | 160 | 90 | 40 |

表2 消費電力の比較

HyperRAM™エコシステムの新しい力

従来のSDRAMとPSRAMは成熟しているため、新たなIoTアプリケーション向けに最適化されることはほとんどありません。車載や産業用アプリケーションの長期供給要件を考慮しても、ウィンボンドのHyperRAM™の先端プロセスノードは、顧客の長寿命製品ライフサイクルに対応することが可能です。

システム全体の設計と製品寿命の観点から、HyperRAM™は新興のIoTデバイスにとって理想的な選択と言えます。サイプレスのほか、NXP、ルネサス、ST、TIなどの大手MCU企業はすでにHyperBus™インターフェースをサポートするMCUを提供しており、今後も各社の新製品がそのサポートを継続していきます。

一方で、制御インターフェースの開発プラットフォームも準備ができています。ケイデンスやシノプシスもHyperBus™メモリ制御IPの提供を開始しており、ICベンダーの設計サイクルの短縮が可能です。 その結果、他のOctal RAMと比較してみても、HyperRAM™は最も成熟したアプリケーション環境を備えています。HyperRAM™はJEDEC規格に組み込まれ、JEDEC xSPI互換テクノロジーとなっています。

ウィンボンドのHyperRAM™製品ラインの現況は下記(表3)の通りです。

| 32Mb | 64Mb | 128Mb | |

|---|---|---|---|

| KGD | ✓ | ✓ | |

| 24TFBGA (6 x 8㎟) 車載グレード提供可能 | ✓ | ✓ | ✓ |

| 49WFBGA (4 x 4㎟)小型フォームファクタ | ✓ | ✓ | ✓ |

| 15WLCSP(1.48x2mm2) | ✓ |

表3 HyperRAM™製品ライン

小型フォームファクタのBGA品はコンシューマー向けウェアラブル市場に最適です。ウィンボンド・エレクトロニクスは20年以上のDRAM製造経験を活かし、お客様のニーズを満たすため、未来を見据えた高性能製品を提供し続けます。